Meeting the challenge of larger, more complex SoCs to address today’s ever-increasing computing demands.

Modern system-on-chip (SoC) design architectures are evolving rapidly, driven by a variety of factors. Traditional SoC design methodology partitions key design components into proprietary, differentiated accelerators or cores alongside reusable, standards-based IP components and subsystems. Until recently, SoC designs were implemented as monolithic designs with all design elements – both proprietary and licensed- integrated into a single piece of silicon. Today, this monolithic approach is evolving to a more disaggregated, or ‘sum of chiplets’, approach.

This evolution is facilitated by several developments that have helped address the challenges of increasingly complex SoCs. Monolithic silicon approaches now often bump up against silicon manufacturing reticle limits, outstripping the capabilities of Moore’s Law scaling. In addition, advanced-node silicon takes far longer to reach mature yields and requires longer design cycles. Not only are wafer manufacturing cycles getting longer, but intrinsic silicon wafer costs are increasing and the rising cost per transistor (CPT) has begun to outweigh the benefits of technology scaling that historically have come with advancements in process technology. Today’s SoC designers must be far more judicious in deciding which design elements to move to the next node and which to maintain in older nodes to achieve a more scalable cost and development framework.

The rise of chiplets

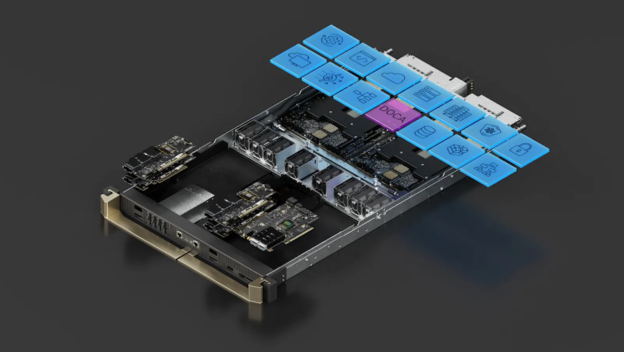

To address these challenges, designers now employ multi-die strategies, using chiplets, to develop large system SoCs. This involves disaggregating the SoC into smaller subsystem die serving different functions, which are matched to the most appropriate process node. Breaking an SoC into separate components helps to solve the issues of design complexity, design cycle times, die size, yield and time to market.

The semiconductor ecosystem, including foundries, EDA companies, SoC providers, and assembly and packaging companies, has begun exploring chiplet designs due to the decreasing silicon economies of scale. Many semiconductor manufacturers have discovered that chiplets make building systems faster and cheaper than monolithic or even prior multi-die solutions.

When properly architected, chiplets provide greater product flexibility, allowing teams to focus on their unique value-add while reducing risk and minimising costs. The chiplet value proposition is akin to silicon IP, which is now ubiquitous in today’s SoC designs.

Chiplets allow SoC providers to leverage design partners for advanced-node designs. Designers can develop entire product roadmaps built around a library of chiplets, resulting in better portfolio management. Complex IP integration can be achieved faster with outright reuse, outsourcing, or minor modifications to an existing chiplet without completely modifying an entire design. There are also important verification and post-silicon advantages to chiplets and disaggregated designs that go beyond just manufacturing realisation. Designers can leverage the extensive software partner ecosystem through reference designs and utilise off-the-shelf chiplets to build products.

The ability to mix and match chiplets is a major win for SoC manufacturers, making it easier to customise products and upgrade product lines. In the future, we will see designs assembled with chiplets from different companies and enabled by industry die-to-die interconnect standards, such as Universal Chiplet Interconnect Express (UCIe). Using chiplets, companies can adeptly respond to changing market dynamics and new technologies, delivering more advanced consumer products more quickly and maintaining a competitive edge.

The drive for differentiation in the More-than-Moore era, especially through multi-die solutions, is gaining momentum and enabling new technologies. As part of this drive, Cadence ensures our IP is scalable to cater to most system requirements. From data centre computing to automotive applications and every segment in between, we have developed strategies to tackle the More-than-Moore challenge with comprehensive solutions spanning the entire technological spectrum. With Cadence’s assistance on the underlying technology, designers can focus on getting their products to market faster and more efficiently.

SoCs and multi-chip systems are growing larger and more complex to accommodate today’s ever-increasing computing demands. As a result, transmitting data within and between silicon components is becoming more challenging, which in turn affects power, performance, and area (PPA). Efficient network-on-chip (NoC) interconnects to manage these multiple high-speed communications across the various cores and IP blocks are vital. Cadence’s Janus NoC is a milestone in our long-term IP strategy to enable customers to build differentiated designs. Cadence combines SoC design expertise, a rich IP portfolio, and leading EDA capabilities to enable more efficient chip design solutions – so companies can do more with limited resources.

With the rise of AI and data centre integration, chiplets’ disaggregation creates new opportunities for silicon design companies. Designers can create systems that deliver new experiences and meet customer demands from a power, performance, and cost perspective. IP in chiplet design is critical; however, customers often need more than just IP to achieve their design goals. Designers need assistance with building subsystems based on advanced chiplet architectures as well.

Your design partner

This is where a trusted design partner plays a crucial role. With our acquisition of Invecas in early 2024, Cadence is well-positioned to be the SoC design partner for our customers developing chiplet-based designs.

The proliferation of AI and 2.5D/3D technologies brings greater SoC and package design challenges for those new to disaggregation. SoC providers need experienced teams to help move designs from ideation to production. Cadence can effectively scale our system design engineering offerings to support customers in critical high-growth verticals, partnering to increase their performance while aggressively tackling ever-increasing system-level complexity.

Cadence’s Silicon Solutions Group is streamlining chiplet design to make it more efficient and by understanding our customers’ needs, we help them stitch together the right chiplets and verify them robustly within a package. Cadence excels at providing the necessary IP and the tools to offer comprehensive 3D-IC design solutions, such as the Cadence Integrity 3D-IC Platform. Going forward, designing for packaging, die-level thermals, and power management is a first-order problem requiring the most advanced tools possible. Cadence is a leader in this domain, bringing together not only IP and tools for thermal and power management but also the necessary test and analysis flows for SoCs and entire systems. These solutions enhance design efficiency, enabling higher bandwidth, reducing power consumption, and supporting seamless die integration across various 2.5D and 3D design applications

Cadence and Arm are collaborating to deliver a chiplet-based reference design and software development platform to accelerate time to market for software-defined vehicles. Initially developed for advanced driver assistance systems (ADAS) applications, the automotive reference design specifies a scalable chiplet architecture and interface interoperability to promote industry-wide collaboration, enable heterogeneous integration and expand system innovation.

Customised silicon is driving most of the transformative technology innovations we are witnessing today, not only in the automotive market, but also in the data centre, AI, consumer, and other markets. Given the rapid pace of technological advancement, the need for novel semiconductor industry solutions, like chiplets, has never been greater. The shift toward chiplet-based designs will only increase as SoC providers seek an edge to remain competitive and more quickly respond to market changes.

With so many tools and opportunities available, 2025 promises to be an exciting time for the semiconductor industry.

https://www.newelectronics.co.uk/content/outlook/outlook-2025-embracing-the-chiplet-journey/